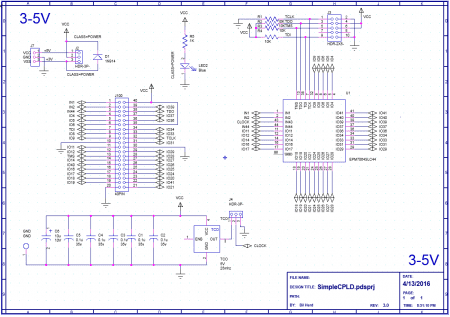

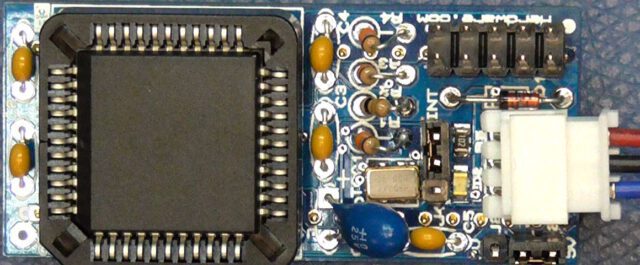

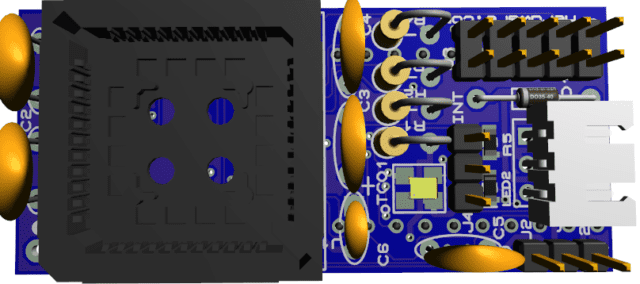

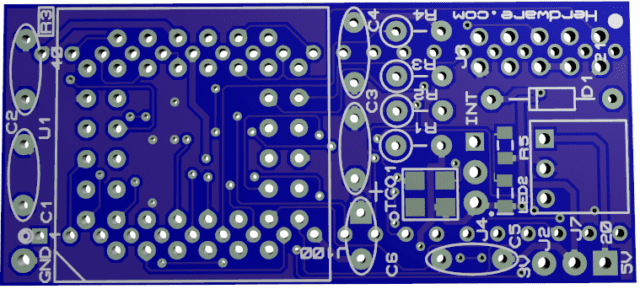

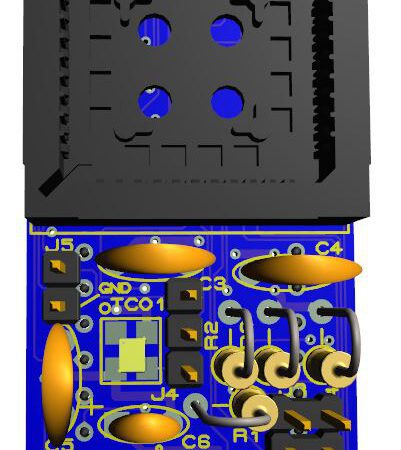

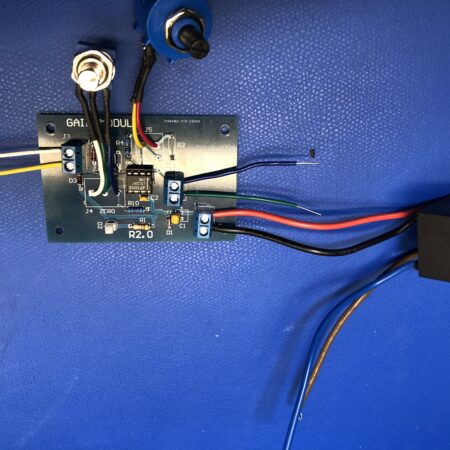

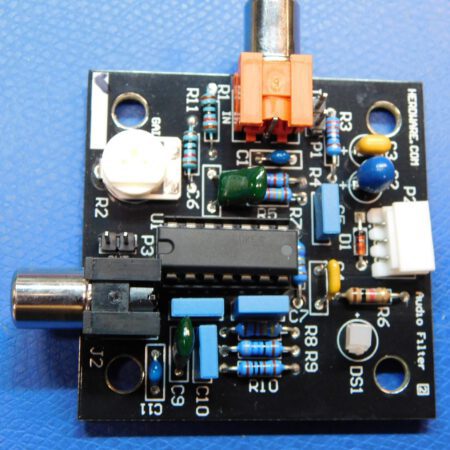

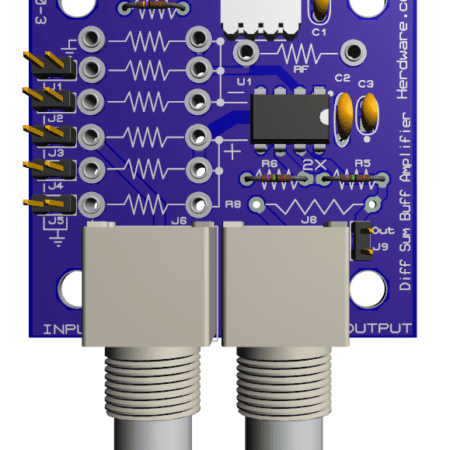

Experiment with programmable logic with this CPLD or replace a logic function or obsolete part. This 40 pin module provides 28 programmable I/O pins and 3 dedicated inputs and can be powered either from the board it plugs into or from the built in multi-voltage power connector.

- Supports EPM7064 CPLDs from Altera

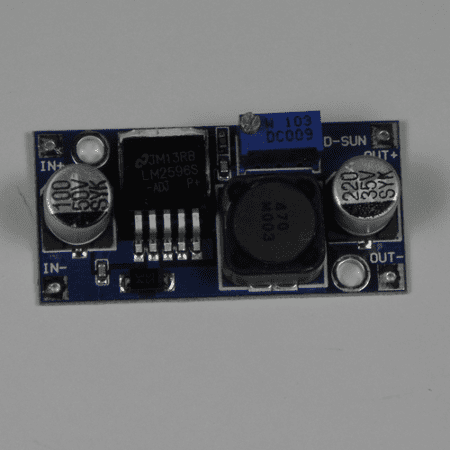

- Power Connector supports 3.3V or 5V voltage selection.

- Has built in multi-volt oscillator or external oscillator.

- Support external supply on three pin connector

- Mostly through-hole construction for DIY assembly.

- Comes as kit or with pre-soldered SMT devices or completely assembled.

- Complete first project to get the beginner up and running quickly.

- Free Development Software: Altera Quartus 9.1

- Complete Demo Design U1 – Design

- In Circuit Programmable

- Jumper selectable between 3.3V and 5V when using Herdware 3 pin power cable

- Use with Herdware 3.3V/5V Mini USB Power Supply

CPLD Module Device Selection:

Altera EPM7064SLC44 +5V ONLY

Altera EPM7064AELC44 +3.3V ONLY

Altera MAX CPLD 7000ADescription

MAX 7000A (including MAX 7000AE) devices are high-density, highperformance devices based on Altera’s second-generation MAX architecture. Fabricated with advanced CMOS technology, the EEPROMbased MAX 7000A devices operate with a 3.3-V supply voltage and provide 600 to 10,000 usable gates, ISP, pin-to-pin delays as fast as 4.5 ns, and counter speeds of up to 227.3 MHz. MAX 7000A devices in the -4, -5, -6, -7, and some -10 speed grades are compatible with the timing requirements for 33 MHz operation of the PCI Special Interest Group.

MAX700A 3.3V Features:

- High-performance 3.3-V EEPROM-based programmable logic

devices (PLDs) built on second-generation Multiple Array MatriX

(MAX®) architecture - 3.3-V in-system programmability (ISP) through the built-in

IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface with

advanced pin-locking capability - MAX 7000AE device in-system programmability (ISP) circuitry

compliant with IEEE Std. 1532 - EPM7128A and EPM7256A device ISP circuitry compatible with

IEEE Std. 1532 - Built-in boundary-scan test (BST) circuitry compliant with

IEEE Std. 1149.1 - Supports JEDEC Jam Standard Test and Programming Language

(STAPL) JESD-71 - Enhanced ISP features

- Enhanced ISP algorithm for faster programming (excluding

EPM7128A and EPM7256A devices) - ISP_Done bit to ensure complete programming (excluding

EPM7128A and EPM7256A devices)

– Pull-up resistor on I/O pins during in-system programming - Pin-compatible with the popular 5.0-V MAX 7000S devices

- High-density PLDs ranging from 600 to 10,000 usable gates

MAX 7000A devices use CMOS EEPROM cells to implement logic functions. The user-configurable MAX 7000A architecture accommodates a variety of independent combinatorial and sequential logic functions. The devices can be reprogrammed for quick and efficient iterations during design development and debug cycles, and can be programmed and erased up to 100 times.

MAX 7000A devices contain from 32 to 512 macrocells that are combined into groups of 16 macrocells, called logic array blocks (LABs). Each macrocell has a programmable-AND/fixed-OR array and a configurable register with independently programmable clock, clock enable, clear, and preset functions. To build complex logic functions, each macrocell can be supplemented with both shareable expander product terms and highspeed parallel expander product terms, providing up to 32 product terms per macrocell.

MAX 7000A devices provide programmable speed/power optimization. Speed-critical portions of a design can run at high speed/full power, while the remaining portions run at reduced speed/low power. This speed/power optimization feature enables the designer to configure one or more macrocells to operate at 50% or lower power while adding only a nominal timing delay.

MAX 7000A devices also provide an option that reduces the slew rate of the output buffers, minimizing noise transients when non-speed-critical signals are switching. The output drivers of all MAX 7000A devices can be set for 2.5 V or 3.3 V, and all input pins are 2.5-V, 3.3-V, and 5.0-V tolerant, allowing MAX 7000A devices to be used in mixed-voltage systems. MAX 7000A devices are supported by Altera development systems, which are integrated packages that offer schematic, text—including VHDL, Verilog HDL, and the Altera Hardware Description Language (AHDL)—and waveform design entry, compilation and logic synthesis, simulation and timing analysis, and device programming. The software provides EDIF 2 0 0 and 3 0 0, LPM, VHDL, Verilog HDL, and other interfaces for additional design entry and simulation support from other industry-standard PC- and UNIX-workstation-based EDA tools. The software runs on Windows-based PCs, as well as Sun SPARCstation, and HP 9000 Series 700/800 workstations

Additional information

| Weight | 0.1 lbs |

|---|---|

| Dimensions | 2 × 1 in |

| Pre-assembled | Yes – Assembled, No – Kit Form, SMT Parts Pre-Soldered, PCB Only |

| CPLD-Voltage | 7064LC-5V 7064AELC-3.3V |

You must be logged in to post a review.

Reviews

There are no reviews yet.